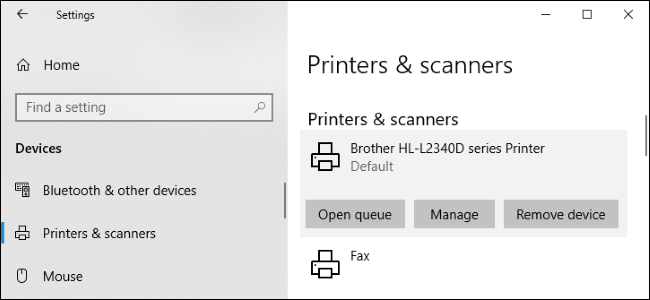

यदि आप सीखना शुरू कर रहे हैं कि मल्टी-कोर सीपीयू, कैशिंग, कैश सुसंगतता और मेमोरी कैसे काम करती है, तो यह पहले थोड़ा भ्रमित हो सकता है। इस बात को ध्यान में रखते हुए, आज के SuperUser Q & A पोस्ट में एक जिज्ञासु पाठक के प्रश्न का उत्तर है।

आज का प्रश्न और उत्तर सत्र सुपरयूज़र के सौजन्य से आता है - स्टैक एक्सचेंज का एक उपखंड, जो कि क्यू एंड ए वेब साइटों का एक समुदाय-संचालित समूह है।

प्रश्न

सुपरयूज़र रीडर कार्मेलो यह जानना चाहता है कि सीपीयू का कैश मुख्य मेमोरी में कब वापस आ जाता है:

अगर मेरे पास दो कोर वाला सीपीयू है और प्रत्येक कोर का अपना एल 1 कैश है, तो क्या यह संभव है कि कोर 1 और कोर 2 दोनों एक ही समय में मेमोरी का एक ही हिस्सा कैश करें? यदि यह संभव है, तो मुख्य मेमोरी का मूल्य क्या होगा यदि Core1 और Core2 दोनों ने अपने मूल्यों को कैश में संपादित किया है?

मुख्य मेमोरी में सीपीयू का कैश कब वापस आ जाता है?

उत्तर

सुपरयूजर योगदानकर्ता डेविड श्वार्ट्ज, सलेस्के और किम्बर्ली डब्ल्यू का जवाब हमारे लिए है। सबसे पहले, डेविड श्वार्ट्ज:

अगर मेरे पास दो कोर वाला सीपीयू है और प्रत्येक कोर का अपना एल 1 कैश है, तो क्या यह संभव है कि कोर 1 और कोर 2 दोनों एक ही समय में मेमोरी का एक ही हिस्सा कैश करें?

यदि ऐसा नहीं होता तो हां, प्रदर्शन भयानक होगा। एक ही कोड को चलाने वाले दो धागों पर विचार करें। आप उस कोड को L1 कैश में चाहते हैं।

यदि यह संभव है, तो मुख्य मेमोरी का मूल्य क्या होगा यदि Core1 और Core2 दोनों ने अपने मूल्यों को कैश में संपादित किया है?

पुराना मूल्य मुख्य मेमोरी में होगा, जो कोई फर्क नहीं पड़ेगा क्योंकि न तो कोर इसे पढ़ेंगे। कैश से संशोधित मूल्य को खारिज करने से पहले, इसे मेमोरी में लिखा जाना चाहिए। आमतौर पर, कुछ प्रकार के MESI प्रोटोकॉल प्रयोग किया जाता है। एमईएसआई के पारंपरिक कार्यान्वयन में, यदि एक कैश में एक मूल्य को संशोधित किया जाता है, तो यह उसी स्तर पर किसी अन्य कैश में बिल्कुल भी मौजूद नहीं हो सकता है।

Sleske से जवाब द्वारा पीछा किया:

हां, दो कैश कैश होने से एक ही मेमोरी क्षेत्र हो सकता है और वास्तव में एक समस्या है जो व्यवहार में बहुत अधिक होती है। उदाहरण के लिए, विभिन्न समाधान हैं:

- दो कैश यह सुनिश्चित करने के लिए संवाद कर सकते हैं कि वे असहमत नहीं हैं

- आपके पास किसी प्रकार का पर्यवेक्षक हो सकता है जो सभी कैश की निगरानी करता है और तदनुसार उन्हें अपडेट करता है

- प्रत्येक प्रोसेसर मेमोरी क्षेत्रों की निगरानी करता है जिसे उसने कैश किया है, और जब वह एक लिखने का पता लगाता है, तो वह अपने (अब अमान्य कैश) को फेंक देता है

समस्या को कैश सुसंगतता और कहा जाता है विकिपीडिया लेख विषय पर समस्या का एक अच्छा अवलोकन और संभव समाधान है।

और किम्बरली डब्ल्यू से हमारा अंतिम उत्तर:

आपके पोस्ट के शीर्षक में प्रश्न का उत्तर देने के लिए, यह निर्भर करता है कि कैशिंग प्रोटोकॉल क्या है। यदि यह राइट-बैक है, तो कैश केवल मुख्य मेमोरी में वापस आ जाएगा जब कैश कंट्रोलर के पास पहले से ही कब्जे वाले स्थान पर एक नया कैश ब्लॉक डालने के अलावा कोई विकल्प नहीं होगा। पहले जिस स्थान पर कब्जा था उसे हटा दिया जाता है और उसका मान वापस मुख्य मेमोरी में लिखा जाता है।

अन्य प्रोटोकॉल राइट-थ्रू है। उस स्थिति में, कभी भी कैश ब्लॉक स्तर पर लिखा जाता है n स्तर पर इसी ब्लॉक n + 1 यह अद्यतित है। यह कार्बन पेपर के साथ एक फॉर्म को भरने के लिए अवधारणा के समान है; जो भी आप शीर्ष पर लिखते हैं वह नीचे दी गई शीट पर कॉपी किया जाता है। यह धीमा है क्योंकि इसमें स्पष्ट रूप से अधिक लेखन कार्य शामिल हैं, लेकिन कैश के बीच के मूल्य अधिक सुसंगत हैं। राइट-बैक स्कीम में, केवल उच्चतम स्तर के कैश में किसी विशेष मेमोरी ब्लॉक के लिए अधिकतम अप-टू-डेट मूल्य होगा।

स्पष्टीकरण में कुछ जोड़ना है? टिप्पणियों में विचार व्यक्त करो। अन्य टेक-सेवी स्टैक एक्सचेंज उपयोगकर्ताओं से अधिक जवाब पढ़ना चाहते हैं? पूरी चर्चा धागा यहाँ देखें .

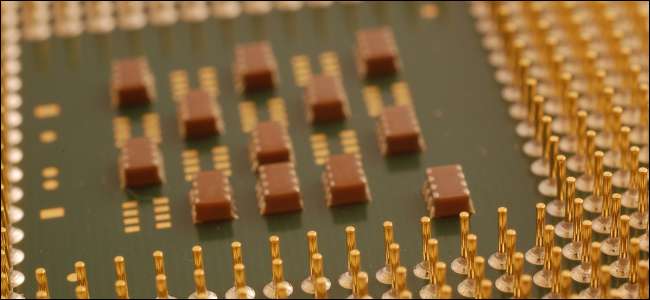

छवि क्रेडिट: लेम्सिपमट (फ्लिकर)