Dacă abia ați început să aflați cum funcționează procesoarele multi-core, cache-ul, coerența cache-ului și memoria, poate părea puțin confuz la început. Având în vedere acest lucru, postarea de astăzi a SuperUser Q&A are răspunsuri la întrebarea unui cititor curios.

Sesiunea de Întrebări și Răspunsuri de astăzi ne vine prin amabilitatea SuperUser - o subdiviziune a Stack Exchange, un grup de site-uri web de întrebări și răspunsuri bazat pe comunitate.

Intrebarea

Cititorul SuperUser CarmeloS vrea să știe când memoria cache a procesorului este întoarsă în memoria principală:

Dacă am un procesor cu două nuclee și fiecare nucleu are propria cache L1, este posibil ca Core1 și Core2 să cache aceeași parte a memoriei în același timp? Dacă este posibil, care va fi valoarea memoriei principale dacă Core1 și Core2 și-au editat valorile în cache?

Când memoria cache a procesorului este readusă în memoria principală?

Răspunsul

Contribuitorii SuperUser David Schwartz, sleske și Kimberly W au răspunsul pentru noi. În primul rând, David Schwartz:

Dacă am un procesor cu două nuclee și fiecare nucleu are propria cache L1, este posibil ca Core1 și Core2 să cache aceeași parte a memoriei în același timp?

Da, performanța ar fi teribilă dacă nu ar fi cazul. Luați în considerare două fire care rulează același cod. Doriți codul respectiv în ambele cache-uri L1.

Dacă este posibil, care va fi valoarea memoriei principale dacă Core1 și Core2 și-au editat valorile în cache?

Vechea valoare va fi în memoria principală, ceea ce nu va conta, deoarece niciun nucleu nu o va citi. Înainte de a scoate o valoare modificată din cache, aceasta trebuie scrisă în memorie. De obicei, unele variante ale Protocol MESI este folosit. În implementarea tradițională a MESI, dacă o valoare este modificată într-un cache, nu poate fi prezentă deloc în niciun alt cache la același nivel.

Urmat de răspunsul de la sleske:

Da, dacă aveți două cache-uri, aceeași regiune de memorie se poate întâmpla și este de fapt o problemă care apare mult în practică. Există diverse soluții, de exemplu:

- Cele două cache-uri pot comunica pentru a se asigura că nu sunt de acord

- Puteți avea un fel de supraveghetor care monitorizează toate cache-urile și le actualizează în consecință

- Fiecare procesor monitorizează zonele de memorie pe care le-a memorat în cache și, atunci când detectează o scriere, își aruncă memoria cache (acum nevalidă)

Problema se numește coerență cache și Articol Wikipedia pe subiect are o imagine de ansamblu frumoasă a problemei și a posibilelor soluții.

Și răspunsul nostru final de la Kimberly W:

Pentru a răspunde la întrebarea din titlul postării, depinde care este protocolul de cache. Dacă este scris înapoi, memoria cache va fi spălată înapoi în memoria principală numai atunci când controlerul cache nu are de ales decât să pună un nou bloc cache în spațiul deja ocupat. Blocul care anterior ocupa spațiul este eliminat și valoarea acestuia este scrisă înapoi în memoria principală.

Celălalt protocol este scris. În acest caz, oricând blocul cache este scris la nivel n , blocul corespunzător la nivel n + 1 este actualizat. Conceptul este similar cu completarea unui formular cu hârtie carbon dedesubt; orice scrieți deasupra este copiat pe foaia de mai jos. Acest lucru este mai lent, deoarece implică în mod evident mai multe operații de scriere, dar valorile dintre cache sunt mai consistente. În schema de scriere, doar cache-ul de cel mai înalt nivel ar avea cea mai actualizată valoare pentru un anumit bloc de memorie.

Aveți ceva de adăugat la explicație? Sună în comentarii. Doriți să citiți mai multe răspunsuri de la alți utilizatori ai Stack Exchange? Consultați aici firul complet de discuție .

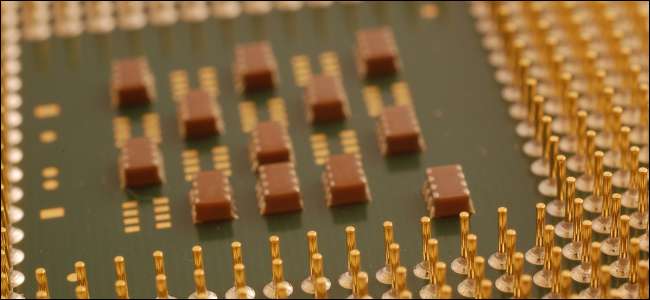

Credit de imagine: Lemsipmatt (Flickr)