Als u meer te weten komt over hoe besturingssystemen en de hardware waarop ze draaien, werken en met elkaar omgaan, zult u misschien verbaasd zijn om te zien wat er op het oog eigenaardigheden of onderbenutting van "bronnen" lijkt te gebeuren. Waarom is dat? De SuperUser Q & A-post van vandaag biedt het antwoord op de vraag van een nieuwsgierige lezer.

De vraag- en antwoordsessie van vandaag komt tot ons dankzij SuperUser - een onderdeel van Stack Exchange, een community-gedreven groepering van Q & A-websites.

Foto met dank aan Lemsipmatt (Flickr) .

De vraag

SuperUser-lezer AdHominem wil weten waarom x86-CPU's slechts twee van de vier ringen gebruiken:

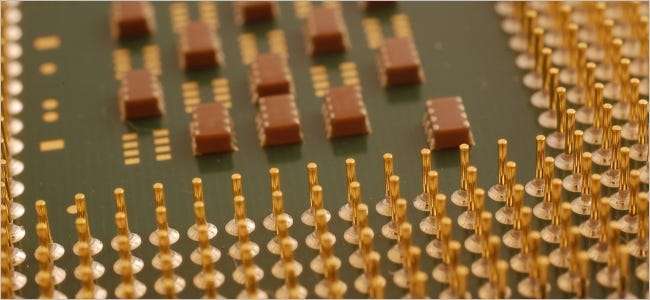

Op Linux en Windows gebaseerde x86-systemen gebruiken alleen Ring 0 voor kernelmodus en Ring 3 voor gebruikersmodus. Waarom onderscheiden processors zelfs vier verschillende ringen als ze er uiteindelijk toch maar twee gebruiken? Is dit veranderd met de AMD64-architectuur?

Waarom gebruiken x86-CPU's slechts twee van de vier ringen?

Het antwoord

SuperUser-bijdrager Jamie Hanrahan heeft het antwoord voor ons:

Er zijn twee hoofdredenen.

De eerste is dat, hoewel de x86-CPU's vier ringen van geheugenbescherming bieden, de granulariteit van de bescherming die daardoor wordt geboden alleen op het niveau per segment is. Dat wil zeggen dat elk segment kan worden ingesteld op een specifieke beltoon (privilege-niveau) samen met andere beveiligingen, zoals schrijven uitgeschakeld. Maar er zijn niet zoveel segmentbeschrijvingen beschikbaar. De meeste besturingssystemen willen een veel fijnere granulariteit van geheugenbescherming, zoals… voor individuele pagina's.

Voer dus op paginatabel gebaseerde bescherming in. De meeste, zo niet alle, moderne x86-besturingssystemen negeren min of meer het segmenteringsmechanisme (voor zover ze in ieder geval kunnen) en vertrouwen op de bescherming die beschikbaar is tegen de lage-orde bits in paginatabelinvoer. Een daarvan wordt het "geprivilegieerde" bit genoemd. Deze bit bepaalt of de processor zich in een van de "geprivilegieerde" niveaus moet bevinden om toegang te krijgen tot de pagina. De "bevoorrechte" niveaus zijn PL 0, 1 en 2 . Maar het is maar één bit, dus op het pagina-voor-pagina-beschermingsniveau is het aantal beschikbare "modi" wat betreft geheugenbescherming slechts twee: Een pagina kan toegankelijk zijn vanuit de niet-geprivilegieerde modus, of niet. Dus slechts twee ringen. Om vier mogelijke ringen voor elke pagina te hebben, zouden ze twee beschermingsbits in elke paginatabelvermelding moeten hebben om een van de vier mogelijke ringnummers te coderen (net als de segmentbeschrijvingen). Maar dat doen ze niet.

De andere reden is een verlangen naar portabiliteit van het besturingssysteem. Het gaat niet alleen om x86; Unix heeft ons geleerd dat een besturingssysteem relatief draagbaar kan zijn voor meerdere processorarchitecturen, en dat het een goede zaak was. En sommige processors ondersteunen slechts twee ringen. Door niet afhankelijk te zijn van meerdere ringen in de architectuur, hebben de uitvoerders van het besturingssysteem de besturingssystemen draagbaarder gemaakt.

Er is een derde reden die specifiek is voor de ontwikkeling van Windows NT. De ontwerpers van NT (David Cutler en zijn team, die door Microsoft werden ingehuurd bij DEC Western Region Labs) hadden uitgebreide ervaring met VMS; In feite behoorden Cutler en een paar van de anderen tot de oorspronkelijke ontwerpers van VMS. En de VAX-processor waarvoor VMS is ontworpen, heeft wel vier ringen (VMS gebruikt vier ringen).

Maar de componenten die in VMS's draaiden Ringen 1 en 2 (Record Management Services en de CLI, respectievelijk) werden weggelaten uit het NT-ontwerp. Ring 2 in VMS ging het niet echt om de beveiliging van het besturingssysteem, maar om het behouden van de CLI-omgeving van de gebruiker van het ene programma naar het andere, en Windows had dat concept niet; de CLI werkt als een gewoon proces. Wat betreft VMS's Ring 1 , de RMS-code in Ring 1 moest bellen Ring 0 vrij vaak, en ringovergangen zijn duur. Het bleek veel efficiënter te zijn om gewoon naar toe te gaan Ring 0 en er klaar mee zijn in plaats van er veel van te hebben Ring 0 overgangen binnen de Ring 1 code (nogmaals, niet dat NT in ieder geval zoiets als RMS heeft).

Wat betreft waarom x86 vier ringen implementeerde terwijl besturingssystemen ze niet gebruikten, heb je het over besturingssystemen met een veel recenter ontwerp dan x86. Veel van de systeemprogrammeerfuncties van x86 werden ontworpen lang voordat NT of echte Unix-achtige kernels erop werden geïmplementeerd, en ze wisten niet echt wat het besturingssysteem zou gebruiken. Pas toen we paging op x86 kregen, konden we echte Unix-achtige of VMS-achtige kernels implementeren.

Moderne x86-besturingssystemen negeren niet alleen segmentering grotendeels (ze stellen alleen de C-, D- en S-segmenten in met een basisadres van 0 en een grootte van 4 GB; F- en G-segmenten worden soms gebruikt om te verwijzen naar de belangrijkste datastructuren van het besturingssysteem. ), negeren ze ook grotendeels zaken als "taakstatus-segmenten". Het TSS-mechanisme was duidelijk ontworpen voor het wisselen van threadcontext, maar het blijkt te veel bijwerkingen te hebben, dus moderne x86-besturingssystemen doen het "met de hand". De enige keer dat x86 NT hardwaretaken wijzigt, is voor een aantal echt uitzonderlijke omstandigheden, zoals een dubbele foutuitzondering.

Met betrekking tot x64-architectuur zijn veel van deze niet meer gebruikte functies weggelaten. Het strekt tot hun eer dat AMD daadwerkelijk met kernelteams van het besturingssysteem heeft gesproken en gevraagd wat ze nodig hadden van x86, wat ze niet nodig hadden of niet wilden, en wat ze graag zouden willen toevoegen. Segmenten op x64 bestaan alleen in wat zou kunnen worden genoemd rudimentaire vorm, het wisselen van taakstatus bestaat niet, enz., En besturingssystemen blijven slechts twee ringen gebruiken.

Iets toe te voegen aan de uitleg? Geluid uit in de reacties. Wilt u meer antwoorden lezen van andere technisch onderlegde Stack Exchange-gebruikers? Bekijk hier de volledige discussiethread .